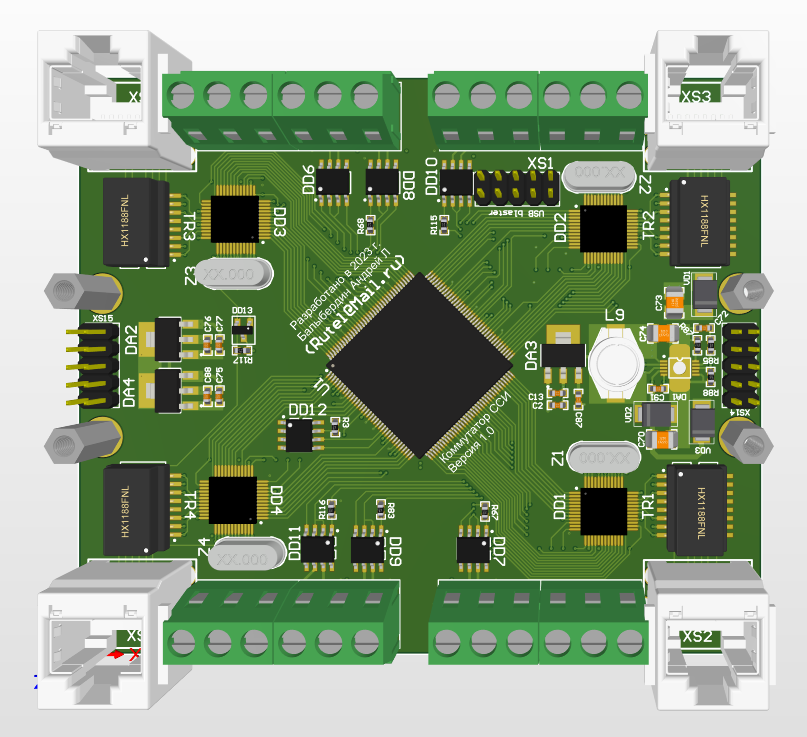

Выполнено проектирование тестовой версии коммутатора ССИ.

Запущено изготовление, предварительный срок готовности март 2023г.

Есть 4 канала 100Мбит и 6 каналов RS485 + разъемы для установки плат расширения.

Назначение:

1. Для изучения базовых принципов ССИ.

2. Исследования в рамках сетей реального времени для систем автоматизации.

3. Работы по проектированию распределенной операционной системы реального времени.

Комментарии

Проект выходного дня для старшеклассника.

Зачем это здесь?

Формально, это блоги. В блогах можно примерно все что угодно в рамках здравого смысла и УК РФ. Плюс, человек не толкает разработку, а скорее микрорекламится, но с посылом что его работу можно использовать в любых целях

Это для "некоторых" кто говорит, что я только литературным творчеством занимаюсь.

Попробуйте на досуге сделать что-нибудь работоспособное на частотах 100+ МГц

Если ТС удастся загрузить все каналы Ethernet и RS-485, чтоб с любого Eth получить доступ к любому RS-485, то это не так просто, даже на уровне шлюза

Modbus TCP -> Modbus RTU

А тут не просто можно все загрузить,так еще и в реальном времени определять что какой то пользователь не полностью задействовал выделенный ему канал и пускать по нему асинхронный трафик (трафик без гарантии скорости до, времени доставки или вообще доставки).

КПД использования канала 98% (оставшиеся 2% используются для кодирования).

И вот это по вашему результат? Всё верно сказали, уровень старшеклассника.

Плата сделана для вчерашних старшеклассников.

Надеюсь на скорый "стартап" с интелом (предварительное общение было).

Бедный интел, у них и так проблемы...

Что принципиально новое внедряют только в такие моменты.

Во все остальное время нужно эксплуатировать свои преимущества и превращать их в деньги.

А Вы сколько сделали тестовых стендов для студентов?

Скольких специалистов Вы обучили?

Сколько аппаратуры для коммерчески успешных проектов Вы сделали?

Результаты Ваших работ показывали по центральному каналу в новостях ?

Сколько действительно научных работ Вы написали ?

Вопросом на вопрос? Видать за живое задел.

Есть интересное психологическое наблюдение:

Тот кто не может выделиться сам, делает это за счет попыток "утопить" того кто может.

Вы до психологии ещё не доросли.

Я знаю чего вы так нервничаете - Вы чувствуете, что скоро Вас "выпнут" на мороз как проф-непригодного.

Думаю это очень хорошо - пару лет работы таксистом пойдет на пользу.

Почему таксистом - больше ничего делать вы не можете (по крайней мере ВЫ не предоставили результат)

А после сомнений в компетентности научного учреждения которое связано с вашим работодателем и подавно.

Мельчают "специалисты", если раньше могли аргументированно доказать свою правоту используя научные термины то сейчас уже нет.

Наверное Вы таких слов даже не знаете, не то что ими пользоваться

Когда вы пишите "уровень старшеклассника" вы видимо подразумеваете что 99.9% старшеклассников могут не хуже?

Или 1%?

Подразумеваю, что ТС на самом деле дилетант с самомнением , пользующийся АШ как площадкой, где он может излагать свои опусы. Я почитал его на других форумах, зрелище жалкое.

а слабо это доказать на примере моих текстов и используя научную лексику

Вот два текста:

https://aftershock.news/?q=node/1096748

https://aftershock.news/?q=node/1096761

Кроме того Вы хотите оскорбить уважаемых организаторов "Национального супер-компьютерного форума" ?

https://aftershock.news/?q=node/1185709

А Вы сами то не зарвались в своем величии ?

Пхах.

Ну сами захотели.

Угу ошибся ))

Спасибо что поправили.

___________________________________

Нихрена себе ошибся. Температуру кипения воды с прямым углом перепутал.

Такая ошибка в самом предмете открытия говорит о многом.

____________________________________________________________________

Она говорит просто про орфографическую ошибку "плезиосинхронная" слова нет.

Хота в переводе значит почти синхронный - вполне.

_______________________________________________

На самом деле всё гораздо сложнее. И хуже.

Ты зарегистрировался на специализированном сайте. И первой твоей темой была простыня про то, что ты якобы разработал некую "идеальную сеть". Вторая твоя тема - тоже простыня про какой-то "компьютер пятого поколения". В других темах ты не участвуешь. Твои темы к тематике сайта относятся как "а поговорить". Поскольку во-первых, здесь собрались практики, а во-вторых, твои разработки уже рецензировали умные люди и оказалось, что ничего мало мальски полезного там нет. Не более, чем общие слова и мутные теории.

То есть, зарегился ты явно не для участия в жизни этого форума.

Далее.

Эти же простыни ты выложил на других форумах. Проводить исследования или писать работы по данному предмету ты не хочешь. Вариант патентования отвергаешь.

Можно сделать вывод, что ты просто ищешь возможность потрындеть с теми, кто по обсуждаемому вопросу не имеет глубоких знаний. Потому что кто имеет - сразу раскусил фуфел, несмотря на обилие умных слов в тексте.

На других форумах тебя ещё не послали?

Во круть...

На хабре ТС тоже попустили. Там у него вот что висит:

"О себе

Лавочка закрыта по причине отсутствия конструктивного диалога с сообществом."

__________________________________________

Ах, да, кстати. Как там Китайские товарищи?

Опубликовано 15 февраля, 2021 · Жалоба

Да, я и решаю - сейчас общаюсь с китайскими "товарищами",

да и если подумать зачем "Российским" инженерам теоретические знания

если последние 70 лет Российская электроника разрабатывается методом

наклеивания этикетки поверх "буржуинских" микросхем.

______________________

Плавно эволюционировали в Интел?

Думали я что, тупенький и не пробью вас?

На форумах временами такую хренатень несут... Вообще не аргумент.

Разбирать вас дальше мне лень. Что такое научные конфы и телевидение я знаю. Светиться там большого ума не надо, скорее наоборот умные там не водятся.

Я не просто знаю что это такое, а двадцать лет назад реализовал полностью отвечающий стандарту приемо-передатчик E1 (со всеми сигнализация сверх-циклами и тд) и это через пять лет после завершения учебы

https://www.analytic.ru/articles/lib225.pdf

Слово плезиосинхронный (plesio - означает почти) есть - это последня степень асинхронности перед полностью синхронной системой. Для стандарта передачи данных PDH правильно говорить плезиохронная - там точность не такая строгая (по этому поводу есть стандарт, а в Е1 есть механизм называемый стаффиг битами)

Вы не научный специалист - Вас не интересует истина.

Иными словами Вы говорите, я участвую в научных проектах, но я знаю что то (судя по тону) нехорошее про научные конференции и участвующих в них ученых.

А Вам не кажется, что это "попахивает" откровенной проституцией ?

без перехода на личности - можно сказать в чем бесполезность проекта от ТС? Я свой первый синтезатор звуковых частот сваял на первом курсе месяц бегая по барахолкам. Только на последнем курсе удалось что-то сделать на DSP. В промежутке было только ваяние всяких моделей по методу переменного состояния на паскале. Если сейчас все старшеклассники такие крутые как я на пятом курсе - снимаю шляпу, но по факту этого не наблюдаю. Даже хуже - спроси любого старшекласника что-то сваять на машинных кодах, ассемблере и С (а это основа писать микрологику) - впервый раз услышат.

А что не так-то? Вполне результат. Из таких результатов и растет всё остальное. Что вам не нравится?

Тут все просто, я со своей "медвежьей косолапостью" наступил на "мозоль" вот и вредничает.

Жена на меня ругается - весь народ распугаешь со своим характером.

Сразу говорю

не корысти радине со зла, а только прогресса ради.А в качестве центрального чипа что?

FPGA Cyclone I (EP1C6-TC144) - то что осталось из хлама от старых проектов (с деньгами проблема).

Altera ещё свой софт не прикрыла?

Что используете в качестве PHY? Или ещё лучше дайте ВОМ-файл, чтоб оценить проект

Наверное, много этих "из хлама" осталось незапаянных? На всех студентов хватит?

Плата еще не запущена - предупреждаю могут быть проблемы.

Кому нужна схема (pdf) или проект для альтиум пишите на Rutel@Mail.ru

Даже не сама разводка интересует(там вполне могут быть ошибки), а на чём реализовано, то есть просто перечень микросхем.

Может, укажите чипы DD1, DD6, DD12 ?

RTL8201BL для 100МБит (есть вопрос сколько байт idle вставлять что бы микросхема думала что передаются стандартные пакеты)

MAX485 для RS-485.

По 485 интерфейсу есть "задумка" как подключать сеть ССИ к любому контроллеру без аппаратных переделок (просто повесить обработчик прерываний) и формировать из практически любого числа таких контроллеров распределенную систему реального времени с надежностью свойственной систем применяющим "троирование".

MAX485 - очень легко убивается микросхема.

Лучше выбрать DIP-корпус и устанавливать на колодке.

В корпусе SO-8 RS-485 практически все одинаковые - MAX485 на момент покупки была самой дешевой в ЧИП и ДИП.

То, что самая дешёвая, не сомневаюсь, но они долго не живут, там где постоянная перекоммутация.

Защищайте диодами.

И ещё клеммы под винт тоже плохо живут. Лучше сразу запаять разъёмные. Чтоб реже отвёрткой в плату тыкали.

А в качестве DD12 что используете ?

EPCS4SI8

Родные очень дорого стоят. Иной раз проще простейшую однокристалку для этих целей прикрутить.

резко не вспомню, но есть совместимые аналоги.

А тактовый для EP1C6 с обратной стороны платы? Что-то не вижу. И сколько МГц?

До 100 выводите с помощью PLL или сразу столько на выделенный вход подаёте?

66МГц

RTL8201 25МГц (интерфейс 4 бита за такт)

Вы не планируете поддерживать ARP, ICMP и прочее ?

ССИ это синхронная (не пакетная связь)

А пакетная сети асинхронна по своей сути (нет никаких гарантий) - ну кроме случаев когда пакет имеет одинаковый размер и передается с точно известным периодом (SDH).

Если поток из ССИ попадает в пакетную сеть, то теряется качество обслуживания, все гарантии и тд.

Да можно реализовать шлюз в сеть Ethernet, одно из направлений работы.

С RTL8201BL не сталкивался, только с dp83848 и ip101g

У них у всех четко стандартизованный интерфейс, отличаются в копейках и возможно в своих частных заскоках.

чёрт всегда прячется в частностях.

А каждой PHY свой кварц для надёжности?

Наверное, есть много вариантов, как им 25 МГц подать

Специально -в рамках ССИ есть механизм позволяющий компенсировать не полную синхронность коммутаторов и линий связи.

Вот для тестирования механизма и сделано.

Начинайте пакеты с 6-ти байт со значением FF, не прогадаете. Длину пакета лучше делать кратно 32 битам. Для надёжности. Некоторые железяки плохо относятся к тем, кто так не делает.

Там не все так просто - если я правильно понимаю нужно пропустить минимум два байта (ничего не слать)

Дальше кодер (8D9B) вставит служебную последовательность idle вот по ней и все засинхрится (в документации есть упоминание).

Но это я проверю при отладке.

По идее, вначале нужно

по MDIO/MDCдождаться установления линкаилипо светодиоду(Вам в проекте это будет проще контролировать). И да, между пакетами нужны паузы, чтоб они между собой связь контролировали.возможно так (там автосоединение 100Мбит стоит).

Но мало ли, в какой то момент времени что то произойдет - вот и нужно принудительно ресинхронизировать битовый поток (что бы байты собирались один в один).

А то микросхема подождет какое т о время (время для передачи максимального пакета) и решит что ошибка и остановит прием.

Поток по-любому нужно будет паузами разбавлять. Чтоб хотя бы для PHY казалось, что они с нормальными пакетами работают

Страницы